| Sommaire: |

![]()

Technologie PadLock

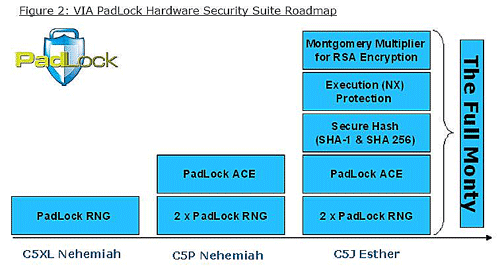

Ne pouvant pas se battre face à AMD ou Intel en terme de performance brute, VIA a choisi une autre voie pour rendre son processeur attractif: la sécurité. VIA a annoncé une suite de fonctions connues sous le nom de "PadLock" dans ces processeurs C5XL et C5P, ces fonctions sont censés apporter une plus grande sécurité à l'utilisateur. PadLock se compose actuellement de 2 éléments: le RNG disponible sur le core C5XL et C5P et l'ACE disponible uniquement sur le core C5P.

RNG (Random Number Generator) : VIA est parti de la constatation que de plus en plus de transactions cryptées se font sur Internet, transactions basées sur des clés. Ces clés sont bien souvent générées par des générateurs de nombres aléatoires (RNG) softwares. Le problème est que d'une manière ou d'une autre les générateurs software ne sont pas totalement aléatoires, il fallait donc trouver une solution complètement aléatoire.

Il existe 3 grandes manières de générer des nombres aléatoires

- Par voie logicielle : cette manière de générer

des nombres est la moins sûre car elle dépend d'un algorithme

codé par un humain. En connaissant les conditions de départ

on peut théoriquement regénérer les mêmes

nombres. Ce sont des générateurs de type "pseudo

aléatoires".

- Par l'utilisation de phénomènes physiques :

c'est cette méthode qui est utilisée par Microsoft ou

le noyau Linux. La génération de nombres se base sur des

phénomènes comme les mouvements de la souris, l'entrée

du clavier, les IRQ ou encore les accès au disque dur. Bien que

très sûre, le caractère aléatoire de cette

méthode ne peut pas être prouvé.

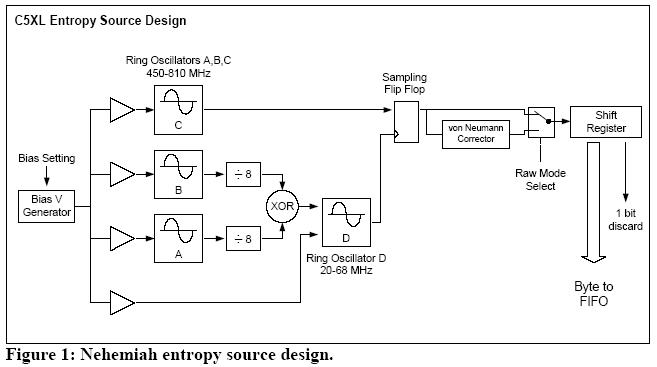

- Par l'utilisation de phénomènes au niveau sub-atomique : le fait de bouger aléatoirement de manière imprévisible est une qualité intrinsèque de toute particule sub-atomique, c'est la source que VIA a choisie pour son générateur de nombres aléatoires. Ce générateur se base sur les instabilités de fréquence de plusieurs oscillateurs que l'on voit dans le schéma ci-dessous.

Dans le C5XL VIA a donc implémenté un RNG qui se base sur le bruit électronique ambiant comme source pour générer des nombres. Les avantages de le solution sont une consommation bien moindre de cycles CPU qu'une solution software et une génération de nombres réellement aléatoires en tout temps. VIA estime que ce RNG est capable de générer entre 1600K et 60M de nombres par seconde suivant la qualité voulue du caractère aléatoire de la chose. Ces nombres sont accessibles par une simple instruction x86 et ont donc le désavantage évident est qu'il faut un support de cet RNG par le software, c'est le cas dans les noyaux Linux 2.6 pour le moment ainsi que de FreeBSD et OpenBSD (peut nécessiter une recompilation). Une application directement programmée pour en tirer parti peut bien sûr également les utiliser, même sans support de l'OS.

ACE (Advanced Cryptography Engine) : cette unité permet d'effectuer des encryptions AES (Advanced Encryption Standard) de manière hardware. Le cryptage AES, développé par deux chercheurs belges, a été choisi par le gouvernement des USA en 2001 afin de remplacer le vieillissant cryptage DES car il dispose d'un algorithme d'encryption amélioré et utilise de plus grandes clés. Le standard AES permet d'encrypter des blocs de 128 bits avec 3 longueurs de clés possibles:

- 128 bits, ce qui nous donne 2128 possibilités

- 192 bits, ce qui nous donne 2192 possibilités

- 256 bits, ce qui nous donne 2256 possibilités

Pour comparaison, l'ancien cryptage DES avait 256 possibilités. Pour mieux se représenter l'amélioration que cela représente, disons que si on pouvait décrypter une clé DES 56 bits en 1 seconde, il faudrait comparativement 149 milliards d'années pour décrypter une clé AES 128 bits. L'unité ACE intégrée dans le C5P est capable de décrypter ou d'encrypter des données jusqu'à 12.8Gb/s avec de multiples accès simultanés par différentes applications et tout ceci sur une surface ne représentant que 0.76 mm².

Le C3 est capable de supporter les 4 modes standards de chiffrement AES:

- ECB (Electronic Code Book)

- CBC (Cipher Block Chaining)

- CFB (Cipher Feedback)

- OFB (Output Feedback)

N'étant pas un expert dans ce domaine, je vous laisse voir une bonne explication de ces modes qui peut se trouver ici. Un driver permettant d'exploiter cette unité existe pour OpenBSD mais comme pour l'unité RNG, n'importe quel logiciel peut y faire appel directement grâce à une instruction x86 étendue.

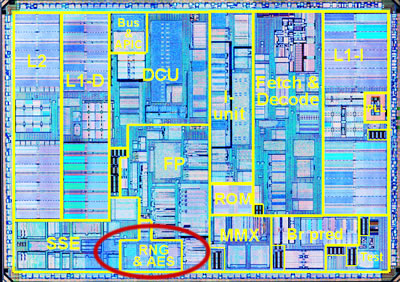

On voit ici une image du core d'un C5P montrant ces 2 unités:

D'ici début 2005, quand le C7 (C5J - Esther) sortira, les fonctions PadLock se verront greffer de nouveaux éléments comme le désormais connu NX-Bit.