| Sommaire: |

Etude détaillée du Pentium-M [1/2]

- Le noyau "P6+"

Comme nous l'avons vu, l'architecture du Pentium !!! est bien adaptée aux processeurs mobiles, et donc logiquement ce noyau qui a servi de base ŕ celui du Pentium-M. Le cpuid du Pentium-M révčle d'ailleurs un processeur de la famille P6, dont le modčle (9) le situe (étonnamment) entre le Coppermine (8) et le Tualatin (11).

Nous constatons en outre le support du jeu d'instruction SSE2 en plus du MMX et du SSE, ainsi que le bus processeur "Quad pumped" ŕ 400MHz.

A titre de rappel, le noyau du Pentium !!! est un noyau RISC ŕ 5 unités de calculs et possédant une pipeline ŕ 10 niveaux. Le noyau du Pentium-M est donc trčs proche, ŕ ceci prčs qu'une inconnue demeure quant ŕ la profondeur du pipeline ; en effet, le Pentium-M est disponible aujourd'hui jusque 1,6GHz, fréquence qui se situe ŕ notre avis au delŕ de ce que permet le pipeline du Pentium !!!, du moins en 0.13µ. Il est donc fortement probable que le pipeline du Pentium-M soit équipé de plus de 10 niveaux, car nous savons que l'inflation du nombre d'étages d'un pipeline permet d'augmenter la fréquence de fonctionnement. Intel semble confirmer cette modification de profondeur du pipeline du Pentium-M, mais sans fournir plus de précisions quant ŕ la profondeur exacte retenue.

Nous pouvons cependant raisonnablement supposer que la valeur se situe plus prčs de 10 que de 20, car l'augmentation du nombre d'étages se paie par une diminution de l'efficacité du traitement, notamment en cas de mauvaise prédiction de branchement. A ce titre, le Pentium 4 a recours ŕ de nombreuses innovations afin d'améliorer le rendement de son trčs long pipeline.

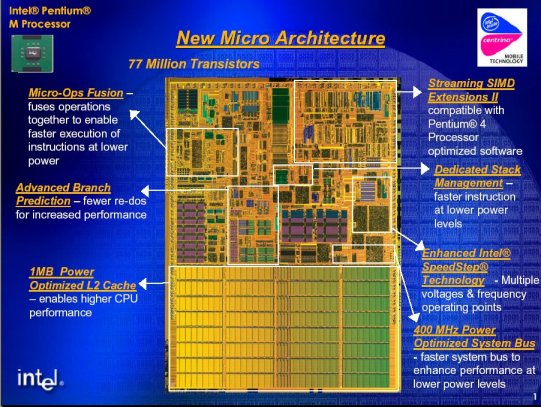

Cette modification du pipeline justifie ŕ elle seule le fait que le noyau du Pentium-M ne soit pas exactement le męme que celui du Pentium !!! et qu'il a nécessité de nouveaux masques. Les modifications apportées ne s'arrętent d'ailleurs pas lŕ, et le Pentium-M innove avec l'apparition de nouvelles techniques d'optimisation, telles que nous pouvons les voir sur ce document fourni par Intel.

Le noyau du Pentium-M

- Une prédiction de branchement améliorée

Si elle permet une augmentation de la fréquence de fonctionnement, l'augmentation

de la profondeur du pipeline est également particuličrement néfaste en

cas de mauvaise prédiction de branchement ; en effet dans ce cas le pipeline

nécessite d'ętre entičrement vidangé, opération d'autant plus coűteuse

que le pipeline est long.

Le Pentium !!! possčde ŕ ce titre deux mécanismes de prédiction de branchement

complémentaires, qui permettent dans de nombreux cas de réduire le nombre

d'échecs de branchement. Le Pentium 4, davantage sensible aux branchements

non prédits, implémente de nombreuses techniques d'optimisation, la principale

étant le Trace Cache qui permet de réduire les pénalités en cas de mauvaise

prédiction.

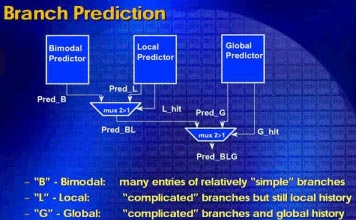

Le Pentium-M n'a quant ŕ lui pas de Trace Cache, mais il améliore la prédiction

de branchement du Pentium !!! et possčde trois mécanismes complémentaires

:

- Le mécanisme statique qui repose sur un algorithme figé et concerne

les branchements simples. Cet algorithme permet de détecter les sauts

qui seront fortement susceptibles d'avoir lieu ou ŕ l'inverse fortement

susceptibles de ne pas avoir lieu. Ce mécanisme est ainsi désigné sous

le terme "bi-modal".

- Un mécanisme de prédiction dynamique dédié aux boucles locales. Un

buffer ŕ portée locale stocke un historique des branches prises et non

prises. Ce systčme est appelé "Local Predictor".

- Un mécanisme de prédiction dynamique semblable au précédent, ŕ la

différence que l'historique est stocké dans un autre buffer dont la

portée est cette fois ci globale. Ce mécanisme concerne donc les boucles

de plus grande taille, et est appelé "Global Predictor".

Les trois mécanismes de prédiction de branchement du Pentium-M

Ces trois mécanismes permettent, selon Intel, de réduire les échecs de prédiction de branchement de 20% par rapport au Pentium !!!.