| Sommaire: |

Présentation des CPU

La première étape pour pouvoir voir l'évolution, c'est de recensé les CPUs dans la course. Sur les 10 derniers classements, on recense 21 types de microprocesseurs :

Power 3 |

PowerPC G5 |

Cray |

Pentium 4 Xeon |

Opteron |

Sparc |

Power 4 |

HP PA-RISC |

Pentium Pro |

Itanium |

MIPS |

Nec |

Power 4+ |

Hitachi SR8xxx |

Pentium 3 |

Itanium 2 |

Alpha |

Athlon MP |

Power 5 |

Fujitsu |

Pentium 4 |

Nous allons présenter chacun de ces CPUs :

- Power 3

- Power 4, Power 4+ & Power 5

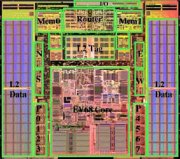

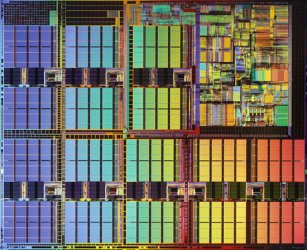

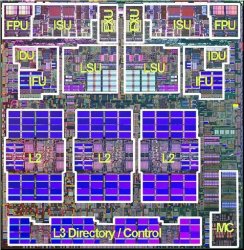

Le POWER 4, sorti en 2001 et gravé en 0.18µm, est le premier CPU bi-core commercialisé. Il contient 2 cores d'éxecution (composés de 2 ALU et 2 FPU ainsi que d'une unité spécifiquement dédiée aux prédiction de branchement) avec leur L1 (32 ko Data & 64 ko Instructions par core), un " Core Interface Unit " qui arbitre l'accès aux 3 caches L2 distincts, mais commun aux 2 cores (une sorte de Triple-Channel) et donne à chaque core un accès aux données absentes du L1 et du L2. Le CPU contient de plus un contrôleur pour de la L3 externe et est, évidemment, prévu pour le SMP. D'un point de vue software, le POWER 4 est vu comme "un simple Bi CPU SMP". Le POWER 4+ est un POWER 4 gravé en 0.13µm et doté de quelques améliorations, mais l'architecture reste la même. Il existe des Chips contenant 4 die POWER4 et leur cache L3 et on peut monter ces puces par 4, globalisant ainsi 32 cores d'éxecution ! Cela démontre les bonnes aptitudes du POWER4 pour le SMP. Le POWER 5, dernier représentant de la famille POWER en date, hérite d'une bonne partie de l'organisation de son prédécesseur. En outre, il dispose du SMT, d'un contrôleur mémoire intégré ainsi que d'un système de virtualisation du processeur (pour faire tourner plusieurs OS sur un seul CPU) |

Power 5 |

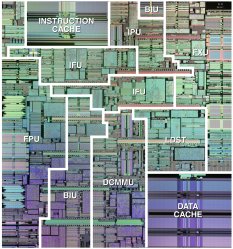

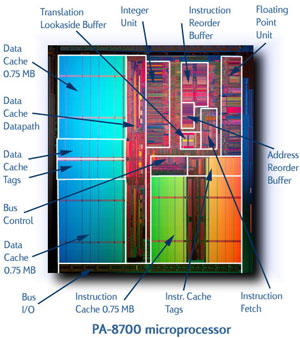

- HP PA-RISC

|

|

L'architecture PA-RISC (Precision Architecture RISC) a été spécifiquement conçu pour fonctionner en SMP sans trop de latence, en intégrant, dès l'origine un cache L1 de taille importante. 32 bits initialement (en 1994), il deviendra 64bits en 1996 avec le PA-RISC 8000. La famille des PA-RISC va s'éteindre à cause du choix d'HP d'utiliser l'Itanium qu'ils ont aidé à développer. Dans les dernières versions, le PA-RISC (PA-8800) contient 2 cores et 1,5 Mo de L1 par core et 32 Mo de L2 commun aux deux cores et utilise le bus des Itanium 2. |

- Hitachi SR8xxx

Processeur RISC 64 bits développé spécifiquement pour les supercalculateurs, l'Hitachi SR8000 est basé sur l'architecture POWER et doté d'extensions pour permettre, notamment, le crossbar "en 3D" pour accélérer les traitement en SMP. De plus les SR8000 sont doté d'un mode "pseudo vector processor" dans lequel ils font du calcul vectoriel "à plusieurs".

- Sun UltraSPARC & Fujitsu

|

Les premières stations Sun étaient équipées de Motorola 680x0, tout comme les Macintosh. Mais vu l'orientation "personnelle" du Macintosh, la suprématie technique des stations sun apparait temporaire. Bill Joy, alors "chef" technologique chez Sun mais surtout ancien élève de Berkeley, rencontre David Patterson qui travaille sur l'architecture RISC. Ils élaboreront le SPARC. Le SPARC, comme tous les CPU RISC, possède un grand nombre de registres (comparés, bien sûr, aux 8 GPR du x86) : plus de 500 registres au total. L'UltraSPARC est la version 64bits du SPARC, désormais propriété d'un consortium indépendant, qui vend des licences et permet d'implémenter sa propre versions de l'UltraSPARC. La dernière version est l'UltraSPARC IV dotée, entre

autres, d'un controleur mémoire intégré (comme

son prédécesseur l'UltraSPARC III), du CMT, d'un pipeline

à 14 étages, et un cache L2 externe (jusqu'à

8Mo) |

|

- MIPS

|

|

Le MIPS (Microprocessor without interlocked pipeline stages) a été lancé au même moment que le SPARC, suite au même constat, mais fait cette fois-ci par Silicon Graphics et James Clark, ancien de Stanford, université dans laquelle on développe, justement, une architecture RISC. Cela donne naissance au MIPS R2000. MIPS implémentera ensuite un RISC 64bits, quasiment au même moment que DEC et son Alpha. Actuellement, MIPS en est au R16000 : 2 ALU, 2FPU (1 ADD et 1 MULTI) et 64ko de L1 et gère jusqu'à 8 Mo de L2 externe. |

- Alpha

L'architecture Alpha a été lancé par DEC et représente le premier CPU 64 bits de l'histoire. Basé sur une architecture RISC et cadencé à 150MHz lors de son introduction, il a longtemps été "le processeur le plus rapide de la planète". Ces puces se sont distinguées dès le début par certaines caractéristiques innovantes: |

|

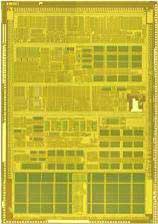

La première version commerciale de l'Alpha est sortie en 1992: le 21064 ou plus communément appelé EV4. Ce nom provient de la technologie CMOS4 (0.75 microns) utilisée pour sa gravure. Cette puce est cadencée à 200MHz, dispose d'une architecture superscalaire et superpipelined. L'EV7 est apparu en 2003 et se compose principalement d'un core EV6 + 2 contrôleurs mémoire RDRAM intégré. Aujourd'hui, Alpha a été vendu à Compaq, lui même racheté par HP. HP a annoncé la fin du développement de l'Alpha, encore une fois pour favoriser l'Itanium 2. Le dernier Alpha sera donc l'Alpha EV7z. Pour plus d'information : Alpha par Steven M. |

|

- AMD Athlon MP

|

|

Processeur x86, l'Athlon est doté de 3 ALU et de 3 FPU, et supporte les instructions MMX et 3DNow!, ainsi que de 24 instructions spécifiques. Il comporte 128 ko de cache L1 et d'un L2 externe (mais dans la cartouche) de 512 ko lors de son introduction en 1999. Il évoluera vers 256ko de L2 on die, et passera de son format "Slot" initial à un format de type "Socket" . Il est également le premier CPU x86 à avoir franchi le gigahertz. Il a évolué ensuite en intégrant le SSE, à partir de la première génération d'Athlon XP, le Palomino gravé en 0.18µm. C'est également l'apparition de l'Athlon MP pour multi processor. L'Athlon MP a continué à évoluer avec l'Athlon XP, jusqu'au Barton, doté de 512 ko de cache. |

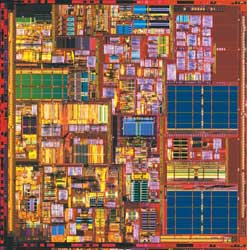

- AMD Opteron (& Athlon64)

Premier CPU x86 64bits, l'Opteron conserve une totale compatibilité (et de très bonnes performances) avec les binaires x86-32 (d'ailleurs si l'OS est 32bits, il fonctionne en 32bits uniquement). Son architecture est très proche de celle de l'Athlon MP. Il ajoute le SSE2, le contrôleur mémoire intégré au CPU pour réduire la latence et le x86-64, qui apporte, en plus de la profondeur plus grande des GPR (64bits), 8 GPR de plus. En contrepartie, en mode 64 bits, il n'est plus possible d'utiliser le x87. Il dispose de 128ko de cache L1 (64ko data et 64 ko instructions) et de 1Mo de L2. L'Opteron dispose de plusieurs liens HT, afin de faire du multiprocesseur de type NUMA (chaque CPU dispose de sa propre RAM, mais peut adresser la RAM "des autres CPU"). Ils existent en mono CPU, bi CPU ou multi CPU. |

|

- Intel Pentium Pro

Premier CPU x86 capable de fonctionner en "Out of Order", uniquement 32 bits et à disposer d'un cache L2 intégré au chip (mais séparé du die), le Pentium Pro est un CISC (comme tous les x86), mais qui décompose les instructions en micro-instructions et les exécute (en interne, c'est un RISC). Il en existe plusieurs versions, allant de 256 ko à 1 Mo de cache L2, et le Pentium Pro a fait preuve de très bonnes aptitudes en SMP. Le Pentium Pro était disponible de 150 MHz jusqu'à 200 MHz. |

- Intel Pentium 3

|

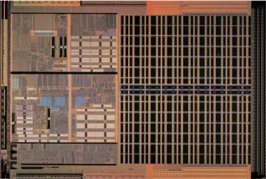

CPU x86 32 bits, le Pentium 2 est un Pentium Pro doté du MMX, extension du jeu d'instructions, de type SIMD, remappant les registres FPU pour fonctionner. Le Pentium 3 est une évolution du Pentium 2 doté des instructions SSE, encore extension de type SIMD du jeu d'instruction, utilisant des registres spécifiques 128 bits. Il en a existé plusieurs versions, qui diffèrent par la taille (de 256ko à 512ko) et la fréquence de leur cache (50% ou 100% de la fréquence CPU). Il existe également des Pentium 3 Xeon, qui peuvent être doté de jusqu'à 2Mo de cache L2

|

|

- Intel Pentium 4 & Xeon

Architecture x86, Netburst est au coeur des Pentium 4 et Pentium 4 Xeon. Elle introduit un cache L1 d'instructions qui stocke, non pas les instructions, mais les microinstructions (décodées). A sa sortie, Netburst est décliné en core Willamette, aux performances déplorables et doté de 256 ko de cache L2. Il donnera aussi les Xeons core Foster. Le core Northwood qui l'a suivi est bien plus performant, et est la base des cores Prestonia et Gallatin (respectivement Xeon DP et Xeon MP), doté de 512 ko de cache L2 et suivant les cas, jusqu'à 4 Mo de cache L3. Il a introduit aussi au cours de sa "carrière" le SMT, nommé Hyperthreading. Le core Prescott, qui a donné le Nocona (Xeon DP), est quant à lui doté de 1 Mo de cache L2.

|

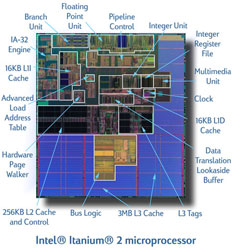

- Intel Itanium & Itanium 2

|

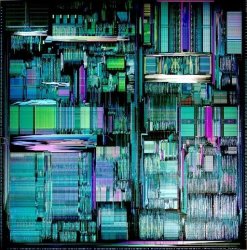

Nouvelle génération d'architecture concue par Intel et HP, EPIC ( Explicitly Parallel Instruction Computing) est un modèle RISC qui bannit le "out of order" (par rapport au code compilé). L'ordre dans lequel les instructions ont été placés par le compilateur est celui dans lequel les instructions seront exécutées. La seule prédiction de branchement qui lui reste est celle inhérente aux conditions d'exécutions, si le compilateur n'a pas pu les éviter dans son ordonnancement. Il se distinue par de très bonnes performances en FPU sur les applications developpés et compilés pour lui et des performances déplorables en x86. Sur l'Itanium 2, au cours d'une de ses révisions, l'unité IA32 a été remplacé pour une émulation software qui donne de meilleures performances. Il dispose d'un cache L1 de 32ko (16ko Data + 16ko Instructions), un L2 de 256ko et un L3 de 3 à 9Mo pour l'instant (24Mo en prévision). |

- Cray & NEC

Les processeurs des Cray X1 sont très atypiques : ils sont composés de MSP (Multi-Streaming Processor), composés de 2Mo de cache et de 4 SSP (Single-Streaming Processor). Chacun de ces SSP est composé de 2 unités vectorielles (32 registres 4"096 bits) à 800MHz et contenant, chacune, 3 unités fonctionnelles "spécialisées" et 1 unité scalaire à 400MHz.

Quant aux microprocesseurs NEC, ils sont developpés spécifiquement pour les supercalculateurs de la marque. Ce sont des CPU de type vectoriel.