| Sommaire: |

![]()

Présentation du chipset (SiS 735)

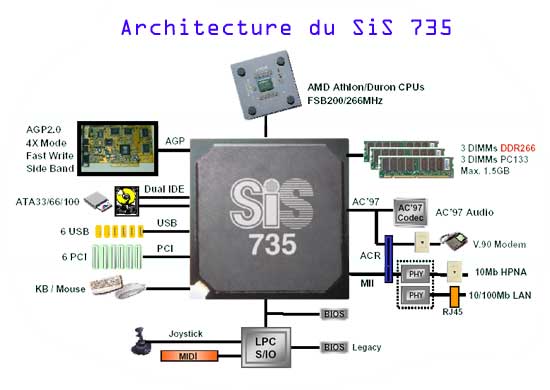

I - L'Architecture du SiS 735

|

Commencons par la premiere chose qui distingue ce chipset de ses principaux concurrents : le SiS 735 n'est constitué que d'un seul composant qui remplis les fonction de Northbridge et de Southbridge ! L'intégration dans un meme composant de ces deux fonctions permet de simplifier le design de la cartes méres et surtout, d'éviter le goulet d'etranglement que représente la communication SouthBridge/NorthBridge. En effet, cette communication s'effectue via le bus PCI, donc avec un débit maximum de 133 Mb/s. Dans sa gamme xx266, Via a introduitun bus propriétaire, le V-Link, permettant un fonctionnement à 266 Mb/s. SiS quant a lui, propose sa technologie MuTiOL qui permet un débit de 1.2 Gb/s !! Cependant, cette performance n'en est pas vraiment une, puisque la communication à cette vitesse ne s'etabli qu'à l'intérieur du SiS 735, l'unique composant. |

|

Comme on peut le voir, le chipset gére les composants suivants :

Le SiS 735 gére donc aussi bien la DDR-SDRAM que

la classique SD-RAM avec un maximum de 1.5 GB ( 3x 512 Mo ) . On retrouve

aussi le support de 6 ports PCI, d'un slot AGP 4x FastWrite et d'un controleur

IDE double-canal UltraATA 33/66/100.

A Noter que les recents Athlon XP sont aussi compatible avec le chipset.

II - La technologie MuTIOL

Comme nous l'avons dit plus haut, le SiS735 est en fait un composant 2-en-1 puisque NorthBridge et SouthBridge sont inclus dans la meme puce. la problématique de la communication etre ces deux elements se voit donc extremement réduite. SiS a donc créé un bus entre ces deux composants internes permettant un échange de données à 1.2 Gb/s ! Cette technologie se nomme MuTIOL, pour "Multi-Threaded I/O Link". Voyons donc un schéma de cette technologie :

Comme on peut le voire le bus systeme interne du SiS est bien plus performant que celui des autres chipsets. Cependant, a-t-on vraiment besoin de 1.2 GB/s dans la communication inter-bridge ? Assurément non. le principal interet est, comme le V-Link, de ne pas surchager le bus PCI avec les echanges inter-chipsets.

Autre point interessant, la technologie utilisé par SiS permet un accés simultanés aux différents éléments géré par le southbridge (principalement le bus PCI et le bus IDE). Ce qui permet d'accroitre la bande passante et donc les performances lorsque plusieurs périphériques sont utilisés simultanément. SiS annonce un gain pouvant aller jusqu'a 35% par rapport a une architecture V-Link. Voici un benchmark en situation réalisé avec Intel IOMeter :

Attention : ces chiffres nous sont fournis par SiS ! Cependant, nous avons réalisés quelques tests rapides dans ce sens et nous sommes arrivés à des résultats similaires.

Concernant les résultats, on voit clairement que les chipsets basés sur une interface PCI pour la communication inter-chipsets sont clairement a la traine, bridé par la bande passante du bus PCI, 133 Mb/s. Ensuite, le V-Link de Via arrive a se maintenir a un trés bon niveau de performances ( du a sa bande passante de 266 Mb/s). En premiere place, on retrouve logiquement le chipset de SiS qui arrive premier, grace a son bus MuTIOL, mais aussi grace à la configuration du test, qui l'avantage beaucoup.