| Sommaire: |

![]()

Présentation type - Chipset SiS 645

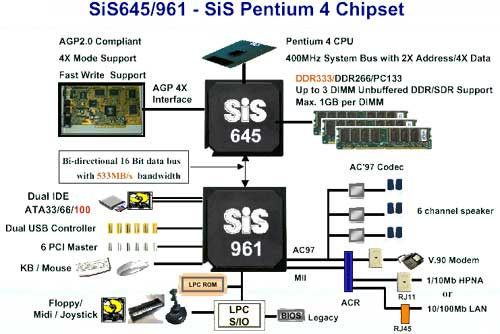

Comme nous l'avons dit dans l'introduction, le chipset SiS 645 est le

premier chipset a gérer la DDR333 dans un environnement Pentium

4. C'est d'ailleurs le premier chipset a gerer la DDR333 tout court. Au

contraire du SiS 735, Sis est revenu au traditionnel couple NorthBridge

/ Southbridge pour ce chipset. Le SiS 645 est donc composé du NorthBridge

SiS645 et du Southbridge SiS961. Nous allons donc séparer cette

partie en deux, mais voyons tout d'abord un schema du chipset représenté

dans sa totalité :

- Le Northbridge : SiS 645

Commencons par le Northbridge. La principale innovation qu'il contient

est la gestion de la DDR333. Etant donnée que le FSB des Pentium

4 est toujours de 100 Mhz QDR et celui de la DDR333 de 166 Mhz, on constate

que le SiS645 est capable de gérer une désynchronisation

entre la RAM et le CPU. Bien entendu, cette solution s'avérera

moins performante qu'un FSB synchronisé à 166 Mhz, mais

Intel ne semble pas vouloir augmenter son FSB a plus de 133 Mhz (qui fera

son apparition avec le Northwood).

Rappelons aussi que le SiS 645 est aussi capable de gerer la SD-RAM classique.

Bien entendu, la SDRAM PC100 / PC 133 et PC166 est supporté par

le chipset, toujours grace a une désynchronisation FSB/RAM.

La capacité maximale que le SiS645 peut gérer est de 3 Go de Ram Unbuffered ( 1 Go maximum par module ) MAIS seul deux slots de DDR-SDRAM peuvent fonctionner en mode DDR333 simultanément. En mode DDR266, un maximum de trois slots peuvent etre utilisé. Bref, la DDR333 a besoin de qualité de transmition optimale pour pouvoir fonctionner correctement avec ce chipset.

Le controleur AGP intégré au NorthBridge gére bien entendu l'AGP 4x et les extentions Fast-Write et SBA (SideBand Adressing). Concernant la gestion de bus à 133 Mhz, aucune information n'est disponible et nous ne pouvons dire si le Northwood sera supporté, ainsi que sa déclinaison à 133 Mhz.

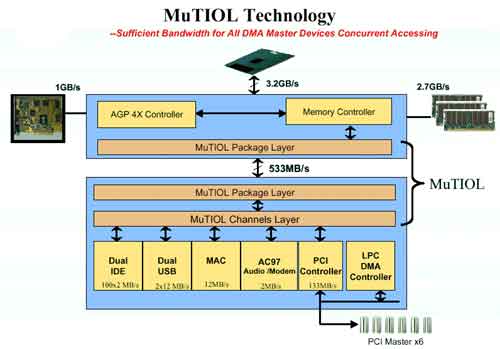

Dernier point à propos de ce Northbridge, somme toute trés

banal (expecté la gestion de la DDR333), la gestion du MuTIOL (Multi-Threaded

I/O Link), la technologie de communication inter-bridge de SiS. le MuTIOL

se place en concurent direct du V-Link de Via. Cepenadant, la technologie

propriétaire de Sis permet une transmition de données à

533 Mb/s, là ou celle de Via est limitée à 266 Mb/s.

Voyons un schema rapide de cette technologie :

Passons maintenant au Southbridge, lui aussi équipé du MuTIOL

- Le Southbridge : SiS 961

Comme nous l'avons vu ci-dessus, le SiS 961 communique avec le SiS 645 via un bus 16 bits (4x66 Mhz) appelé MuTIOL. Le SiS961 est le premier Southbridge généraliste de SiS concu pour la nouvelle génération de chipset. Ce chipset semble efficace sans etre doté de fonctions nouvelles ou innovantes. Il permet la gestion des elements suivants :

- Deux controleurs IDE UltraATA 33/66/100

- Un controleur d'hôte PCI Bus-Master capable de gérer 6 Slots

- Un Double-Controleur OHCI USB 1.1

- Un controleur Audio AC'97 2.2

- Une interface ACR

Meme si ce chipset ne dispose que de fonctions "basiques", il presente tout de meme comme principal avantage de ne pas etre rempli de BUGs divers et variés...