| Sommaire: |

DDR-II : Présentation

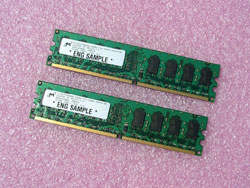

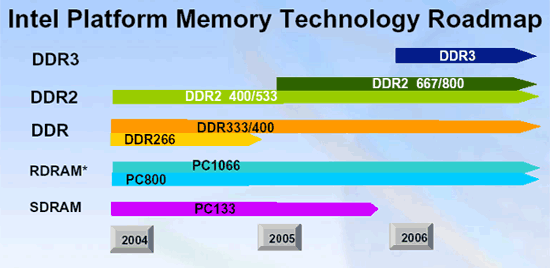

Grande nouveauté de cette plateforme, le support de la DDR-II. Directement remplacante de la DDR-I dans l'évolution des mémoires, la DDR-II a eu des débuts difficiles. Prévue pour 2002 au départ, elle ne sera finalement adoptée en masse qu'en 2005. Conscient de cet état de fait, Intel n'a pu que ce plier aux lois du marché et ajouter le support de la DDR-I en plus de la DDR-II aux i915. Les i925X, quant à eux, étant DDR-II seulement, haut de gamme oblige. Aprés trois générations de chipsets DDR pour Pentium 4 voici donc le passage à la nouvelle génération de mémoire. La DDR-II est désormais produite en masse par tous les grands fondeurs de chips mémoires et on peut déjà trouver en masse sur le marché des modules de Micron et de Corsair. Voyons rapidement l'aspect extérieur de ces modules :

D'une taille identique aux anciens modules de DDR, le nombre de broches à toutefois été augmenté, passant de 184 à 240. De même, l'emploi d'un packaging BGA est maintenant requis alors qu'il n'était que rarement utilisé dans le cas de modules DDR classique. Contrairement au passage SDR vers DDR, le but de la DDR-II n'est pas d'offrir plus de bande passante à fréquence égale que la DDR-I, mais de poursuivre la montée en fréquence. En effet, la DDR-II commencera là ou la DDR s'arrête officiellement, c'est à dire à 200 Mhz (400DDR). Les premiers chipsets comme les i9xx supporteront la DDR-II 400 (PC2-3200), mais également la DDR-II 533 (PC2-4300). De plus, la DDR-II apporte d'autres avantages en terme d'évolution. Ainsi, là ou les modules DDR sont limités à des chips de 1 Gbits, la DDR-II devrait permettre rapidement des modules 2 Gbits et bientôt 4 Gbits, ce qui donne des modules de 8 Go...

- Fonctionnement

Interessons nous maintenant aux points de distinctions entre la DDR et la DDR-II. Les modifications améliorations apportées par la DDR-II face à la DDR-I sont les suivantes :

- Fréquences de fonctionnement / Data Prefetch

- Ajout de Terminaison On-Die

- Calibration OCD

- Augmentation du nombre de banks

- Modification des latences

- Adoption du package BGA

Bref, tout un programme que nous allons maintenant étudier en détail en commencant par la bse

- Fréquences de fonctionnement / Data Prefetch

Etudions maintenant les évolutions en termes de fréquences de fonctionnement de la SDRAM à la DDR-II :

| Commençons par parler de la SDRAM classique. Un module de mémoire est constitué de trois éléments fondamentaux. Le premier est le groupe de cellule mémoire appelée "Memory Cell Array". Viennent ensuite les buffers d'entrée/sortie (I/O Buffer) puis le bus de donnée. Dans le cas de SDRAM PC100, ces trois sous-ensembles fonctionnent tous à 100 MHz. C'est à dire que la cellule mémoire fournit 1 bit mémoires toutes les 10 ns au buffer I/O qui lui même le renvoie sur le bus à une fréquence de 100 millions de bit par secondes (100 MHz). Comme la SDRAM fonctionne sur 64 bits, on obtient une bande passante de (100*64)/8 = 800 Mo/s. Simple. |  |

| Avec l'évolution de la SDRAM, la technique de l'époque limitait la fréquence des cellules mémoires à environ 166 MHz. Le but à donc été de revenir à 100 MHz et de trouver un autre moyen d'exploiter cette fréquence : La DDR PC1600 était née. Si la fréquence du core reste identique, elle renvoie cette fois 2 bits à chaque cycle, on dit alors que le prefetch est de 2 bits. Or, pour que le buffer I/O puisse continuer à travailler à 100 MHz, l'idée d'exploiter les fronts du signal et non plus les états binaires à été retenue. Bref, tout en restant à 100 MHz, la DDR permet de transférer 200 millions de bit par seconde, soit une bande passante de ((100*2)*64)/8 = 1600 Mo/s. | |

| Arrivé à 200 MHz avec la DDR-I, les cellules mémoires commencaient à souffrir. Solution ? Revenir à 100 MHz bien sur ! Mais cette fois, pour maintenir le débit, il fallait doubler la fréquence du buffer I/O. La DDR2 PC3200 exploite donc une fréquence interne des cellules de 100 MHz, ces cellules fournissent 4 bits par cycle au Buffer I/O qui fonctionne cette fois à 200 MHz. Le prefetch passe donc de 2 bits à 4 bits. En sortie, sur le bus de donnée, on obtient ainsi la même chose que de la DDR (exploitation des fronts montants et descendants du signal), mais à une fréquence deux fois plus elevée. Le débit pour une fréquence de base de 100 MHz est donc de ((100*4)*64)/8 = 3200 Mo/s. |

Bref, tout ceci tourne autour d'une modification très importante, qui est le prefetch des données. Comment est-ce possible à un Array de cellules mémoires de fournir 2 ou 4 bits par cycle ? Et bien en le divisant. Si dans le cas de la SDRAM l'Array mémoire était constitué d'un seul et même bloc physique, il est divisé (physiquement) en deux dans le cas de la DDR et en quatre pour la DDR-II :

A noter que l'espacement physique entraine une augmentation de la taille du die d'environ 3%, ce qui n'est pas négligeable (mais pas catastrophique non plus) pour la production. Voyons maintenant les bande passante obtenues avec les différentes générations de mémoire et les fréquence internes du core :

L'intérêt de revenir à 100 MHz pour la fréquence du core est double. Premièrement, ceci permet de monter en fréquence puisqu'on sait que les cores peuvent supporter maintenant plus de 200 MHz, de plus, ceci améliore grandement les yield puisque produire des Array mémoire à 100 MHz ne pose plus de problème pour personne. Ensuite, la faible fréquence de fonctionnement interne permet une consommation électrique plus faible, ce qui n'est pas négligeable pour des mémoires très haute densité.

Continuons maintenant cette étude avec le procédé de terminaisons on-die :

- Ajout de terminaisons On Die

Autre apport important de la DDR-II, les terminaisons On Die. A la manière des périphériques SCSI, la fin de la "chaîne" constituée par les modules de mémoires doit être terminées afin d'éviter les phénomènes de réverbérations du signal qui peuvent se produirent et parasiter tout le sous-système mémoire. Jusqu'à présent, ces terminaisons étaient positionnées sur la carte mères et terminaient la chaîne. Dans le cas de la DDR-II, ces terminaisons sont maintenant inclue directement dans le die du chip et activable à la demande (seul le dernier module doit être terminée). Voyons ça de plus près :

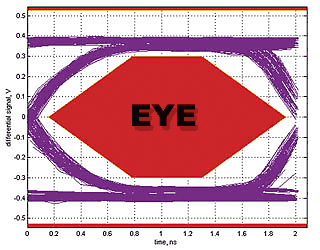

Comme on le voit dans le cas de la DDR-I, les phénoménes de reverberations se produisent alors que dans le cas de la DDR-II, ils sont bien moins nombreux. Ceci permet principalement d'augmenter la fiabilité du signal et donc les fréquences maximales possibles. Dans le cas de la mémoire, on mesure souvent la fiabilité du signal grâce à l'oeil electronique (Eye, en anglais). L'Eye est la partie du signal efficace qui sera lue. Plus il est grand et etendu (on dit "ouvert"), plus le signal sera de bonne qualité. Voici un exemple typique d'Eye :

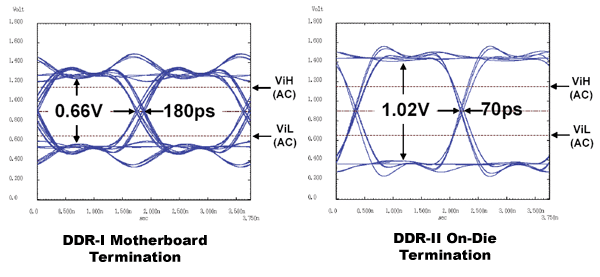

Le losange rouge au milieu symbolise la plage efficace du signal. Pour revenir à notre ODT (On Die Termination), celle-ci sert donc à augmenter l'oeil et donc la plage efficace du signal. Dans le cas de la DDR-II, on constate au vue des mesures comparatives effectuées ci-dessous que le résultat est trés encourageant :

En augmentant la plage de tension et en diminuant les transitions d'état (180 ps pour la DDR-I, 70 ps pour la DDR-II), les terminaisons internes jouent ici très bien leurs rôles. Cet amélioration importante permettra premièrement de monter en fréquence plus facilement, mais permet également une diminution du prix des carte-mères. Les nombreux réseaux de résistances et de condensateurs utilisés pour les terminaisons mémoires ne sont maintenant plus nécessaires.

- Autres modifications architecturales

Voyons maintenant les autres améliorations architecturales apportées par la DDR-II. Il s'agit tout d'abord de parler de l'OCD ou Off Chip Driver Calibration. Chose hardue en vérité, puisqu'expliquer cette technologie de façon simple n'a rien d'évident. En fait, pour simplifier à l'extreme, l'OCD Calibration permet d'eviter qu'un décalage ne se produise entre les différents signaux d'horloge en ajustant l'impedance du buffer. Le but étant que deux signaux inversés se croisent exactement en leur milieu comme on peut le voir sur le graphique ci-dessous :

Les transitions ne sont pas parfaitement synchrones, et ce décalage augmente le temps de transition et donc, diminue la taille de l'eye dont nous parlions au dessus. A noter que l'ajustement est faite via le BIOS et le chipset lors du boot.

Autre point intéressant à noter, la gestion des banques internes aux chips. Si la DDR-I disposait d'une architecture à 4 banks, c'est à dire 4 sections de mémoire indépendante à l'intérieur de chaque chips, la DDR-II disposera de 8 banks internes dés que la taille totale du chip atteindra 1 Gbits et plus. Les performances devraient ainsi être supérieure avec de tel chips. En effet, plus le nombre de banks est grand (surtout sur des chips de grandes capacités), plus le débit peut-être élevé.

Le dernier point à développer est l'évolution des

timings. Concernant le CAS, exit donc les valeurs en .5 puisque dorénavant,

les seules valeurs disponibles officiellement seront 3, 4 ou 5. La majorité

des autres paramètres connus (RAS-to-CAS et RAS Precharge) demeurent

inchangés avec une variation de 3 à 5. Quant au RAS, il

reste variable entre 3 et 15. A noter que, concernant le Write Latency,

celle-ci est dorénavant égale à Read_Latency - 1

alors qu'elle était de 1 CLK quelque soit l'état de Read_Latency

sur la DDR-I. Les timings moyens recommandés pour la DDR-II sont

donc de 4-4-4-13. Les timings agressifs (l'équivalent du bon vieux

2-2-2-5 sur DDR-I), deviennent maintenant 3-3-3-8.

- Passage au packaging FBGA

En effet, là ou les modules DDR utilisaient massivement le TSOP traditionnel, les modules DDR-II ne seront disponibles qu'au format FBGA (Fine Ball Grid Array). Ce packaging dispose en effet de bien meilleure caractéristiques électriques et thermiques que le TSOP :

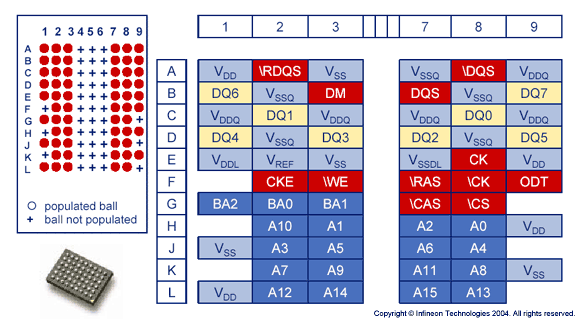

Il permet également des techniques de Die Stacking avancées permettant de coupler plusieurs dies dans le même package afin d'obtenir de plus grandes capacités. Voyons par exemple le ball-out d'un chip mémoire x8 de chez Infineon :

Comme on le voit, au sein même du chip, les pins de données sont bien isolées des autres, ce qui élimine une partie du cross-talk face aux TSOP sur le PCB du module. Ce type de packaging était indispensable pour les débits prévu pour la DDR-II.

- Evolution de la DDR-II

A ce jour, seul les standards DDR-II 400 et DDR-II 533 sont validés. Si, de l'aveu même d'Intel, le passage à la DDR-II 667 ne posera pas beaucoup de problème, il semblerait que la DDR-II 800 ne soit pas disponible avant au moins 1 an 1/2. Le support DDR-II 667 est actuellement prévu dans le chipset LakePort, prévu pour Q2'05. La DDR-III, prévu-elle aussi, ne sera toutefois pas une mémoire de masse avant 2007.

Bref, comme nous l'avons vu, la DDR-II apporte beaucoup d'améliorations techniques à la première génération. Cependant, les débuts à 400 et 533 MHz ne permettent que d'entr'apercevoir le potentiel de cette mémoire. En effet, à ces fréquences, les faibles timings requis pour la montée en fréquence risquent de contrecarrer le gain en performance. C'est ce que nous allons voir tout de suite plus en détails