| Sommaire: |

Vision pour 2015

Récemment, Intel s'est également lancé dans la projection en traçant les grandes lignes de l'évolution des plateformes pour les dix prochaines années. Cette fois, les annonces sont moins sensationnelles que les 10 GHz pour 2005, mais bien plus réalistes. Nous allons donc continuer sur la lancée de la page précédente, mais au lieu d'une spéculation à 2 ou 3 ans, nous allons nous lancer dans le long terme.

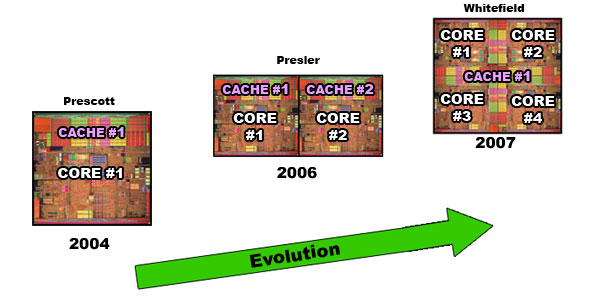

Voyons donc ou nous étions arrêtés :

Pour simplifier, on reste sur des architectures SMP (symétriques) jusqu'a Whitefield, qui devrait faire la transition entre le SMP et l'AMP (Asymétrique). Eh oui, le multiprocesseur, tel que nous le connaissons aujourd'hui, vit ces dernières années. La raison est simple. A l'heure actuelle, les CPUs Dual Core laisseront place aux Quad-Core, puis aux CPUs dotés de 8 cores identiques, toujours sur le même modèle. Ensuite, il va être beaucoup plus complexe d'évoluer, car la multiplication des cores pose rapidement un problème d'efficacité : Une application ne peut se scinder en un nombre illimité de threads, et, passé les 4 ou 8 cores, les gains diminueront pour cette raison. C'est à ce moment qu'apparaitra la deuxième ou troisième génération Nehalem chez Intel, qui marquera un nouveau tournant dans l'architecture des CPUs.

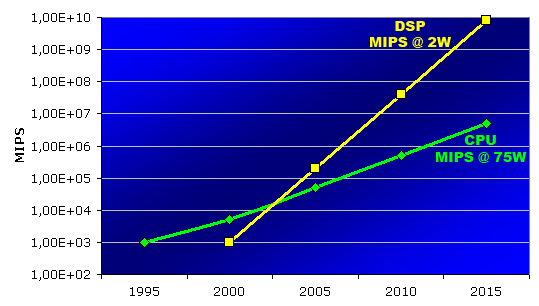

Cette fois, le but sera de combler le manque d'efficacité qui apparaitra forcement avec les cores d'exécutions génériques, tels qu'ils existent actuellement. Le fond du problème est simple : Un CPU peut exécuter un ensemble très vaste de tâche, mais restera toujours largement plus lent d'un DSP spécialisé lorsqu'il s'agit d'effectuer une tache unique et bien précise, et ce, très rapidement. Un petit graphique pour bien comprendre :

Le constat est simple : En 2015, un DSP consommant 2 Watts sera mille fois plus puissant qu'un CPU généraliste consommant 75 Watts. Certes, il ne saura effectuer qu'une seule et unique tâche, mais il la fera très rapidement, tout en chauffant peu. Il ne faut pas réfléchir longtemps pour trouver à quoi ces DSPs pourraient bien servir.

La force de Netburst, à l'heure actuelle, c'est le "content création", c'est à dire toutes les tâches qui nécessitent un énorme débit et qui utilisent des calculs très répétitifs, traité par le Pentium 4 grâce aux unités SIMD que sont MMX et SSE. Or, quoi de plus simple pour un DSP que d'effectuer ce genre d'opérations ? Imaginez un core type Pentium M, ultra performant à basse fréquence, équipé de DSP, eux aussi ultraperformant, pour traiter des instructions de type SIMD. On obtient un processeur cumulant les avantages du Pentium 4 et du Pentium M. Pour peu qu'il dispose de nombreux cores et d'un contrôleur mémoire intégré type Athlon 64, vous obtenez une bête de puissance. Bienvenue chez Nehalem.

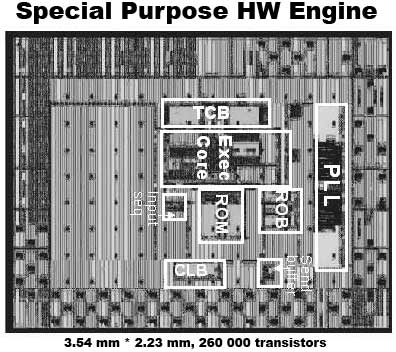

Et ces "super-DSP" sont déjà en court de tests chez Intel pour une inclusion proche dans les futurs CPUs :

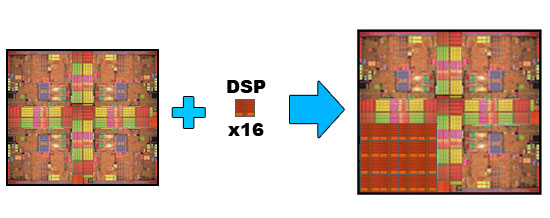

D'une taille ridicule par rapport aux "vrais" CPUs, ces DSP pourraient combler facilement les tâches qui nécessitaient auparavant un long pipeline ou une fréquence élevée, et ce, à une fraction de la puissance électrique requise. On obtiendra donc un CPU de ce type :

Capable de traiter plusieurs instructions généralistes et plusieurs instructions SIMD à une vitesse effroyable, ce type de CPU devrait arriver aux alentours de 2008. Il permettra une évolution nette jusqu'en 2015 par l'ajout de nouveaux cores scalaires du même type. Cependant, une gestion complexe à ce point nécessitera de nouvelle technologie pour éviter que le software ne soit totalement largué et puisse tirer parti de l'énorme puissance disponible.

- CPU 2015 : Technologies annexes

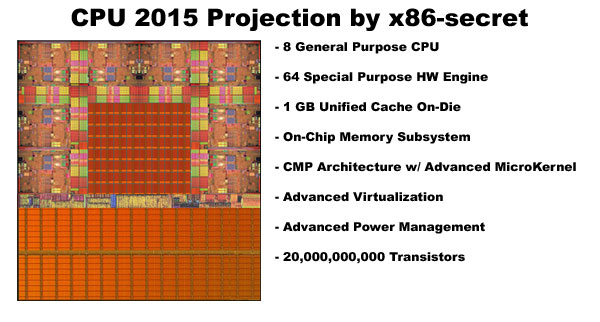

Pour utiliser correctement l'intégralité des ressources disponibles par un processeur dans 10 ans, il faudra penser à de nouvelles techniques de traitement des données. Nous allons ici en expliquer quelques unes. Pour nous aider, nous avons effectué une petite projection graphique de ce à quoi pourrait ressembler un CPU dans dix ans. Exercice quasi-impossible que nous avons réduit à une simple approximation :

L'avenir nous dira si nous étions très loin de la réalité ou pas, mais en attendant, quelques uns des concepts que nous allons définir ici ont de fortes chances de se retrouver un jour dans nos machines. Dans ces concepts, deux sont particulièrement vitaux au fonctionnement de cette plateforme. Si un grain de sable perturbe leurs développements, c'est tout le CPU qui peut être remis en cause. Il s'agit du sous-système mémoire et du MicroKernel. Expliquons ceci de plus près :

- Sous-systéme mémoire

Comme nous l'avons dit, la façon dont sera gérée la mémoire, et le cache en particulier, est primordiale pour le fonctionnement du processeur. Ainsi, les effets de la latence mémoire peuvent totalement annuler un accroissement de la fréquence de fonctionnement par exemple. Côté mémoire donc, exit le lentissime concept de FSB, pour un accès à la mémoire entièrement géré par le CPU, un peu comme sur plateforme K8 actuellement, sauf que les accès seront beaucoup plus performant puisque le contrôleur mémoire gèrera les priorités et les types d'accès pour l'intégralité des cores, généraux et DSP. Pour faire une grossière analogie, on pourrait comparer ce fonctionnement au NCQ des disques dur SATA-II, mais pour la mémoire.

Niveau caches, exit les niveaux de cache Ln et Ln+1 comme à l'heure actuelle, puisque dans cette architecture, une multitude de niveau de cache existeront à tous les niveaux. Les DSP auront leurs caches dédiés, les CPUs auront également leur cache qui, lui, sera probablement partagé, et par dessus tout ceci, une gigantesque mémoire cache on-die fera l'interface entre le CPU et la mémoire (des valeurs comprises entre 256 Mo et 2 Go ne sont pas utopiques). Avec une telle taille, cette mémoire pourra aisément remplacer la mémoire vive pour certaines applications, avec un gain de performances conséquent.

La gestion du cache des CPUs seront également beaucoup plus abouti qu'actuellement. Le cache pourra par exemple être reconfiguré à la volée, avec des zones dédiées à tel ou tel core, à tel ou tel groupe de cores, ou à l'intégralité des cores. Tout ceci sera géré en hardware par le MicroKernel, seconde notion fondamentale.

- Intel CMP et MicroKernel

On le comprend : les futurs CPUs seront horriblement complexes et disposeront de multiples mécanismes leur permettant d'obtenir la quintessence des performances du processeur. Hélas, et c'est une erreur qu'Intel a déjà commis, il serait utopique de croire que les développeurs vont utiliser dans un délai de quelques années, l'intégralité de ces fonctionnalités si celles-ci nécessitent une adaptation majeure des techniques de programmation.

Pour résoudre ce problème qui parait insoluble, Intel a imaginé de déplacer une partie de l'intelligence, comme la gestion des threads, du logiciel vers le matériel : c'est le concept de MicroKernel. En fait, le MicroKernel est une sorte de CPU, dans le CPU, chargé de coordonner et de reconfigurer à la volée les différents composants du processeur. Grâce à lui, la gestion des threads sera effectuée directement en hardware, et retirera ainsi une épine géante du pied des développeurs. Mais ce n'est pas tout, loin de là, le MicroKernel sera capable de :

- Assigner les tâches sur les cores disponibles

- Réassigner dynamiquement un ou plusieurs cores en fonctions de la variation de la charge

- Scinder des threads afin de les paralleliser pour optenir plus de performances

- Scinder ou regrouper les différentes mémoires caches d'une manière optimale

- Desactiver ou réactiver à la volée des cores ou des parties de caches pour économiser l'énérgie

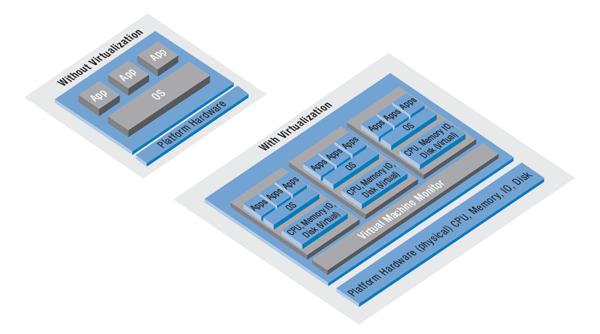

Bref, des capacités très impressionnantes qui vont ainsi retirer une grosse partie de la gestion hardware au kernel du système d'exploitation. Celui-ci devra alors gérer des CPUs et périphériques virtuels, par le biais de machines virtuelles. C'est le but de la virtualisation dont nous risquons de vous brouiller l'écoute dans les mois qui viennent :

Ainsi, le microkernel pourra effectuer une gestion avancée des ressources du CPUs d'une manière totalement invisible pour l'utilisateur, et même pour les programmes qui fonctionnerons sur la machine.

Bref, de très intéressantes perspectives pour l'avenir, qui tranchent clairement avec les semi-progrès pas vraiment révolutionnaires d'Intel depuis 5 ans. Reste maintenant une grande interrogation : Les process de fabrications. En effet, pour atteindre un tel niveau de complexité, avec des dizaines de milliards de transistors, il faudra absolument que les précédés de fabrications suivent. Heureusement, des sommités telles que Mark Bohr devraient rendre tout cela possible, à grand coup de nanotubes en carbones...