| Sommaire: |

Etude des caches L1 / L2

- Le cache L1

Voyons les informations sur les mémoires cache L1 du Pentium-M telles

que renvoyées par les descripteurs de cache.

Les caches L1 du Pentium-M

Le Pentium-M ne comporte pas de Trace Cache (TC) comme sur le Pentium 4, mais un cache code classique de 32Ko. Les caractéristiques des caches L1 des trois processeurs Intel sont regroupées dans le tableau ci-dessous,

| Pentium !!! | Pentium 4 | Pentium-M | |

| Taille | code : 16Ko données : 16Ko |

TC : 12Kµops données : 8Ko |

code : 32Ko données : 32Ko |

| Associativité | code : 4 voies données : 4 voies |

TC : 8 voies données : 4 voies |

code : 8

voies données : 8 voies |

| Taille d'une ligne | code : 32 octets données : 32 octets |

TC : n.a données : 64 octets |

code : 64

octets données : 64 octets |

| Mode d'écriture | Write Back | Write Through | Write Back |

| Latence (données constructeur) |

3 cycles | 2 cycles | 3 cycles |

Les caches L1 du Pentium-M sont trčs similaires ŕ ceux du Pentium !!!,

mais tout y est plus gros. La taille est passée ŕ 32Ko pour les deux caches,

et ils sont désormais gérés en mode asociatif ŕ 8 voies, soit 8 blocs

de 4Ko.

La taille des lignes de cache fait désormais 64 octets, tout comme sur

le Pentium 4. Comme nous l'avons vu dans l'article dédié au Pentium 4,

une ligne de cache de 64 octets se justifie par l'utilisation du jeu d'instruction

SSE et de variables 128 bits ; une ligne trop courte ne permettrait pas

de stocker suffisamment de ces variables et multiplierait les accčs au

cache de niveau inférieur. Et le Pentium !!! me direz vous ? N'oubliez

pas que le cache L1 du Pentium !!! est hérité de celui du PII, et qu'il

a donc été étudié avant l'avčnement des jeux d'instructions 128 bits.

Malgré l'augmentation de la taille des caches, Intel annonce une latence de 3 cycles pour le L1 du Pentium-M, ce que nous aurons l'occasion de vérifier lors des tests de débit et de latence.

- Le cache L2

Le cache L2 du Pentium-M atteint, et c'est une premičre pour un processeur non destiné aux serveurs, 1Mo. Comme on peut le voir sur la photo du noyau, ce cache occupe pas loin de 50 millions des 77 millions de transistors que comporte la puce. Ce cache est de type ATC (Advanced Transfer Cache), tout comme sur les P!!! et P4, et utilise un bus d'interface avec le noyau large de 256 bits. Les descripteurs de cache renvoient les informations suivantes :

Le cache L2 du Pentium-M

Comparons le cache L2 du Pentium-M ŕ celui des Pentium !!! et 4.

| Pentium !!!-S | Pentium 4 Northwood | Pentium-M | |

| Taille | 512Ko | 512Ko | 1024Ko |

| Associativité | 8 voies | 8 voies | 8 voies |

| Taille d'une ligne | 32 octets | 64 octets | 64 octets |

| Latence (données constructeur) |

4 cycles | 7 cycles | 5 cycles |

Toujours géré en 8 voies associatives, le L2 du Pentium-M utilise lui

aussi des lignes de cache de 64 octets. Le cache L2 du Pentium-M est plus

gros mais également mieux géré que celui du Pentium !!!. En effet, le

Pentium-M utilise un mécanisme de prefetching amélioré, dont le principe,

rappelons-le, consiste ŕ précharger en cache des zones mémoires, et ce

afin d'accélérer leur accčs en cas de besoin.

Le prefetching a été inauguré sur le Pentium !!!-S, et sur ce processeur

l'algorithme mis en place ne regarde que "vers le haut", c'est-ŕ-dire

uniquement des adresses situées au dessus de la zone mémoire accédée.

le Pentium 4 a étendu ce mécanisme en permettant de pister simultanément

8 accčs mémoire ŕ des adresses supérieures ("up streaming") ou inférieures

("down streaming"). Le Pentium-M quant ŕ lui est capable de suivre simultanément

8 accčs ŕ des adresses supérieures et 4 accčs ŕ des adresses inférieures.

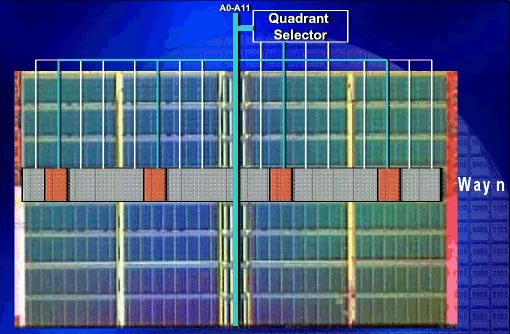

Le cache L2 du Pentium-M possčde une nouvelle caractéristique qui n'est pas mentionnée dans ce tableau, et qui concerne son mode d'adressage.

Dans un cache classique, l'adressage d'une ligne s'accompagne de l'adressage

de tout le bloc qui la contient. Ainsi, pour un cache de 1024Ko organisé

en 8 voies, l'adressage d'une ligne correspond ŕ l'activation d'un bloc

de 128Ko. Or, adresser un bloc consiste ŕ activer toutes les lignes qui

le compose, ce qui consomme de l'énergie, et d'autant plus que le bloc

est gros.

Ce qui peut, avec des blocs de 128Ko, devenir une contrainte de consommation

pour un processeur comme le Pentium-M ! Afin de limiter cet effet, chaque

bloc du cache L2 du Pentium-M est découpé en quatre quadrants, et un sélecteur

de quadrant permet d'en activer un seul ŕ la fois. Ainsi, ce n'est pas

un bloc entier qui est adressé ŕ chaque accčs, mais un seul quadrant de

ce bloc, soit 32Ko.

Le sélecteur de quadrant

Ce systčme permet de réduire considérablement la consommation

du cache L2, mais se fait au détriment des performances, car la sélection

du quadrant représente une étape supplémentaire lors de l'accčs au cache.

Intel annonce ainsi une latence d'accčs au cache L2 du Pentium-M de 5

cycles, ŕ comparer aux 4 cycles de celui du Pentium !!!.

Nous vérifierons bien entendu ces valeurs lors des tests.