| Sommaire: |

Les secrets du Prescott :

Etude du die

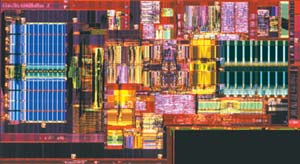

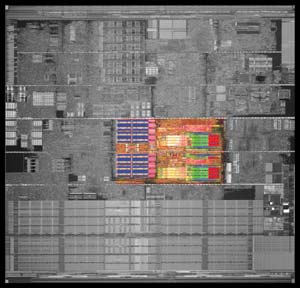

C'est maintenant sûr au vue de la page précédente, le Prescott contient un nombre incroyable de transistors surnuméraires dont l'utilité nous échappe. Pour tenter d'y voir plus clair, nous nous sommes procurés une image haute-résolution du die du prescott et nous allons tenter d'y extraire des informations.

- Mystère Prescott : Le DIE à la loupe

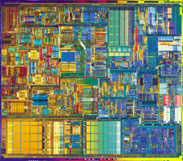

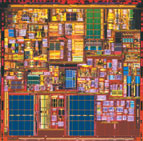

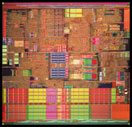

Avant toute chose, voyons une comparaison à l'échelle du die des Pentium 4 0.18, 0.13 et 0.09 µm :

Pentium 4 0.18µm (14.64 mm²) |

Pentium 4 0.13µm (11.45 mm²) |

Pentium 4 0.09µm (10.58 mm²) |

Maintenant, procédons à quelques petits calculs interessants concernant la taille des caches. Nous connaissons la taille d'un côté du die puisque les dies des Prescott et Northwood sont carrés. Sachant que leurs surface est respectivement de 131 mm² et 112 mm², on en dépuis que le côté du carré est égal à la racine de ces valeurs donc 11.45 mm et 10.58 mm. Sachant cela, on peut faire les calculs qui s'imposent sur la surface des caches. Voyons ça :

|

|

On constate ici et après calcul que le cache L2 du Prescott représente 15.06 mm² pour 1024 Ko et que le die du Northwood représente 13.04 mm² pour 512 Ko. Or, dans sa documentation, Intel fournis une information très intéressante et indispensable pour la suite du calcul. Intel indique que la surface utilisée par 1 bit de SRAM était de 2 µm² dans le Northwood et est dorénavant de 1.15 µm² pour le Prescott, soit une réduction de 42.5% (2 - 42.5% = 1.15) entre le Northwood et le prescott.

Ainsi, un espace de 512 Ko qui prenait 13 mm² sur le Northwood n'en prendrait plus que 13.04 - 42.5% = 7.5 mm² dans le Northwood, et comme le Prescott contient deux fois plus de cache, il prendrait 7.5 * 2 = 15 mm² dans le Prescott. Et ça tombe bien, après mesure, c'est effectivement 15 mm² que les 1024 Ko de cache du Prescott consomme en surface ! Le raisonnement est donc bon.

Notre premier sujet d'étude va être le tracecache. Selon Intel, il n'a pas évolué entre le Northwood et le Prescott et reste à 12000 µops. Sachant que le Trace Cache est organisé sous la forme de 4096 lignes de 3 µops, chaque µops d'une taille de 53 bits, ceci nous fait un espace de 80 Ko. Voyons maintenant ce qu'il en est entre le Northwood et le Prescott :

|

|

Le trace cache du Northwood fait donc 2.89 mm² pour 96 Ko. Si sa taille n'a pas évolué, il devrait faire 2.85 - 42.5% = 1.64 mm² dans le Prescott. Or on constate que le Prescott à un trace cache de 2.58 mm², soit environ 58% plus grand. Il contient donc logiquement 55% plus de transistors. On peut ainsi évaluer le trace cache réel du Northwood à 80 + 58% = 128 Ko. Quoi qu'il en soit, le TC du Prescott n'est pas de 12 Kµops comme Intel nous le dit, ou si c'est le cas, la taille des µops a augmenté subitement, ce qui serait indispensable pour un support 64 bits comme l'a déjà dit Hans de Vries ici. Mais le plus impressionnant reste à venir...

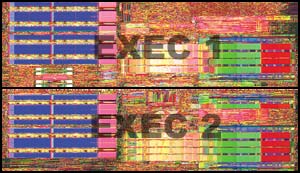

Lorsque nous avons regardé les unités d'exécution

du Prescott, nous avons tout de suite remarqué qu'un double core

d'exécution semblait exister. Sur les photos du die, cette information

saute même au yeux. Voyons ici l'unité d'exécution

d'un Northwood :

Core d'execution - Northwood

On voit ici clairement le cache L1 (en bleu, sur la gauche), les registres (en vert, sur la droite) et l'unité d'exécution (ALU, AGU) qui sont en jaune, entre les deux. Le cache en bleu est un cache de 8 Ko puisqu'il s'agit d'un core d'exécution de Northwood. Concernant le Prescott, voici la preuve du double core d'exécution dont nous vous parlions :

|

|

On voit clairement ici les deux cores d'exécutions, parfaitement symétriques. Pour en être certain, nous avons mesuré la taille d'un seul des blocs de cache L1 (par exemple appartenant au core EXEC1 et l'avoir comparé à celle du Northwood.

Encore une fois, le résultat est surprenant :

|

|

Le cache L1 Data du Northwood mesure 0.8 mm² pour une taille de 8 Ko. Pour la même taille et sur le process 90 nm d'Intel, il devrait faire 0.8 mm² - 42.5% = 0.46 mm², toujours pour 8 Ko. Pour 16 Ko, il devrait donc faire 0.46 * 2 = 0.92 mm². Or, et encore une fois, les calculs sont justes, nous avons mesurés a 0.93 mm² la taille du cache L1 du Prescott. Cependant, et la est tout l'important, on trouve un DEUXIEME cache L1 de 16 Ko juste en dessous du premier ! Preuve que le Prescott contient bien 2 caches L1 et donc forcement deux cores d'exécution. Ainsi, la taille du cache L1 Data total est de 32 Ko, ou plutôt de 16 Ko par core...

- Quelques spéculations

Nous savons maintenant à quoi servent les transistors supplémentaires du Prescott. Cependant, tout comme l'Hyperthreading, ces technologies avancées ne seront pas activées dans l'immédiat, bien que physiquement présentes dans le die dés à présent. Cette double unité d'execution peut servir à plusieurs choses. Premièrement, elle peut servir à une sorte d'HyperThreading 2 qui permettrait des performances proches de celles d'un véritable processeur bi-core. Mais elle peut également servir à traiter des instructions 64 bits... Quant à savoir quand Intel compte activer toutes ces fonctionnalités, c'est une question dont malheureusement, nous n'avons la réponse.