| Sommaire: |

POLISSAGE MECANIQUE ET CHIMIQUE

Les couches ayant besoin d’être créés sur une surface parfaitement plane sont ajustée par un Chemical Mechanical Planarization (polissage mécanique et chimique). C’est un processus qui emploie un abrasif suspendu dans une boue chimique appliquée par des disques rotatifs sur la surface à traiter.

Polissage de la couche d'oxyde isolante

Aprés le polissage, la surface de l'isolant #3 est parfaitement

plane et peu accueillir une autre couche de connexion en Aluminium

L'équipement de polissage peut atteindre 250 000 € !

PHASE 12

LES INTERCONNECTIONS ENTRE COUCHES

Afin d’assurer les interconnections des différentes couches, la couche d’oxyde venant d’être polie est vernie, photolithographiée et excavée pour créer des trous qui seront remplis de tungstène ou de titane-tungstène. Ces connexions appelées plug fournissent le moyen de raccordement électrique entre 2 couches d’aluminium.

La prochaine couche d’aluminium peut être ensuite déposée, vernie puis excavée et ainsi de suite suivant le nombre de couches d'interconnexions nécessaire au wafer. Ainsi, il ne peut y avoir qu’une couche de composants (car il n’y a qu’une epi-couche de silicium) qui sont reliés entre eux par différentes couches d’interconnexion.

PHASE 13

L’INSPECTION DU WAFER

Il s’agit d’une étape critique du processus global de fabrication du wafer. En effet, il doit être inspecté minutieusement à l’aide de différents appareils particulièrement coûteux comme par exemple des MEB (microscope électronique à balayage). Généralement si les différentes phases de conception et le matériel rentre dans les spécifications initiales, l’inspection du wafer ne concernera que l’aspect global du wafer tels que la planéité du wafer ou l’épaisseur des films.

Les dimensions de certaines parties du wafer descendant

en dessous de 0.2µ, l’appareillage de mesure devient de plus

en plus complexe et donc de plus en plus onéreux et la densité

des die augmentant, l’inspection devient de plus en plus longue

et complexe.

Pour inspecter un wafer, rien ne vaut un bon Optima 7200, 15 000 €...

PHASE 14

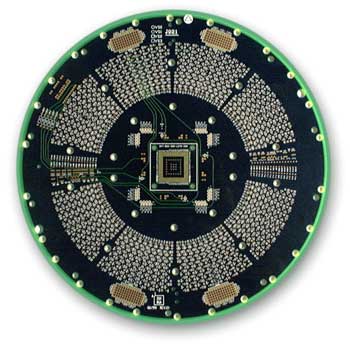

LE TEST

C’est au moment du test ou essai du wafer que l’on observe la correspondance entre le cahier des charges initial et le fonctionnement final du composant. Cette étape nécessite 3 outils de base :

- Un chariot de transport place le wafer dans un mandrin et l’aligne

avec précision sous l’ensemble de contacts constituant

la carte de test.

- Une fine sonde électrique connecte les différentes entrées,

sorties et modules d’alimentation à la carte de test.

- L’appareil de contrôle (ATE : Automatic Test Equipment), vérifie de façon logicielle le fonctionnement global du circuit. A la moindre détection de défaillance, le circuit est immédiatement marqué par un point d’encre

PHASE 15

REPARATION DE REDONDANCE

Ce processus appelé Redundancy Repair est exclusivement utilisé pour des chips de mémoire. On peut comparer cette technique à une simple roue de secours d’automobile. En effet, les die de mémoire sont constitués de matrices qui sont elles-mêmes constituées de colonnes et de rangées.

Pour pallier aux aléas de fabrications, les matrices sont constituées

de colonnes et de rangées supplémentaires, les éléments

défectueux d’une matrice peuvent être remplacés

par ces lignes et rangées de secours. Une fois identifié,

un outil de précision est utilisé pour couper la liaison

sur l’élément défectueux et refaire la liaison

vers l’élément de secours.

Ces éléments de secours font augmenter le coût global

de fabrication mais sont largement rattrapé par l’économie

faite lors de la réparation des éléments défectueux,

car sans ces éléments de secours le die serait

inutilisable.