Processeur : de Nehalem à Haswell

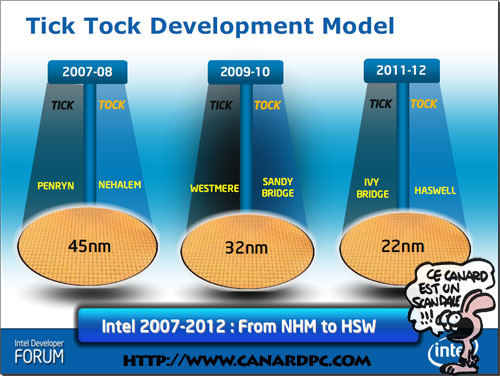

L'IDF est généralement l’endroit idéal pour en apprendre plus sur le cœur de métier d’Intel, c'est-à-dire la conception de microprocesseurs. Bien que cette édition n’ait pas été riche en annonces, nous avons tout de même pu glaner certaines informations en discutant avec des ingénieurs travaillant dans les centres de R&D. Ceux-ci nous ont confiés l’état d’avancement des projets d’Intel pour les 5 prochaines années. Les nouveaux CPU suivront donc le schéma de développement « Tick-Tock », c'est-à-dire une nouvelle architecture tous les deux ans (Tock), suivie d’un die shrink (Tick) consistant à augmenter la finesse de gravure. En exclusivité, voici les noms de code de prochaines générations de processeurs, et ce, jusqu’en 2012 :

Nous sommes actuellement au core "Penryn", le Core 2 gravé en 45 nm. Fin 2008 apparaitra la prochaine génération, toujours gravée en 45 nm, et connu sous le nom de code "Nehalem". Fin 2009, c'est "Westmere" qui prendra la relève. Il s’agira d’une déclinaison de Nehalem gravée en 32 nm. L’histoire se répété ensuite en 2010 avec l’arrivée d’une nouvelle microarchitecture baptisée Sandy Bridge (ex-Gesher) puis de son die shrink en 22 nm : Ivy Bridge. Enfin, en 2012, c’est Haswell qui lui succédera.

Avant de passer aux CPU plus « exotiques », voyons tout d’abord à quoi correspondent ces différentes architectures.

- Nehalem (NHM)

Le prochain changement de microarchitecture interviendra à la fin de l'année avec Nehalem. Ce processeur est actuellement au stepping B1 et nous avons pu obtenir une photo en gros plan du wafer, tenu par Pat Gelsinger Himself.

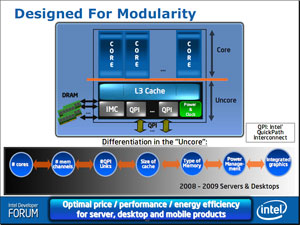

Ce processeur, qui succédera aux Core 2 actuels, se distinguera principalement par sa modularité. En effet, contrairement aux processeurs actuels, il sera possible très facilement de la décliner en de nombreuses versions. Nehalem étant en fait constitué de « blocs » logique, assemblé à la manière de lego. Nombre de cœurs (de 1 à 8), taille du cache, type de contrôleur mémoire intégré, présence d’un cœur graphique, ...etc. seront ajustables par Intel en un minimum de temps, et cela afin de répondre aux besoins. Nehalem sera également doté d’un contrôleur mémoire intégré, à la manière des Athlon 64 et autres Phenom, mais également d’un bus d’interconnexion rapide baptisé QPI.

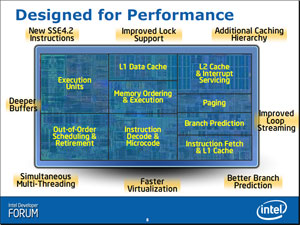

Le cœur d’exécution de Nehalem sera basé en grande partie sur celui du Core 2 actuel, bien que quelques améliorations aient été apportées pour la gestion d’un cache L3 commun. En termes de performances, Nehalem devrait offrir de 15 à 20% de gain par rapport à un Core 2 de fréquence égale. La principale inconnue reste les performances de la plateforme entière, et tout particulièrement du contrôleur mémoire intégré. Nehalem disposera de 32 Ko de cache L1 Data, de 256 Ko de cache L2 à très faible latence par cœur ainsi que d’un cache L3 de taille variable (jusqu’à 8 Mo sur les versions Desktop). Nehalem disposera également de l’Hyperthreading, qui permet d’exécuter 2 threads par cœur. L’efficacité de cette technologique sur ce type d’architecture à pipeline court reste toutefois sujette à caution.

Nous aurons l'occassion très bientôt de revenir sur les multiples améliorations apportées par Nehalem.

- Sandy Bridge (SNB)

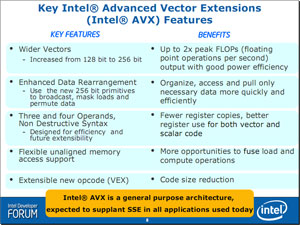

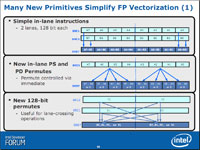

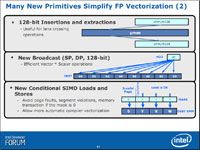

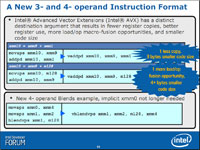

En 2010, l'architecture Sandy Bridge, anciennement appelée Gesher, succédera à Nehalem. Celui-ci devrait être doté de 8 cœurs sur le même die, d’un cache L2 de 512 Ko par cœur et d’un cache L3 de 16 Mo. L’une des caractéristiques principale de Sandy Bridge sera l’ajout du jeu d’instruction AVX (Advanced Vectors Extensions), autrefois connu sous le nom VSSE.

L'arrivée de l'AVX sera probablement aussi marquante que lorsque le SSE est apparu sur les Pentium III en 1999. Les trois points principaux sont :

- L’extension des registres SSE actuels de 128 à 256 bits, tout en restant compatibles avec les instructions SSE 128 bits.

- Le réarrangement avancé de données : une seule opération pourra traiter simultanément 8 données de 32 bits

- La possibilité d’utiliser trois ou quatre opérandes

Intel annonce d’ores et déjà que l’utilisation de l’AVX en lieu et place du SSE accélérera le traitement de certaines opérations comme la multiplication de matrices d’environ 90%.

- Haswell (HSW)

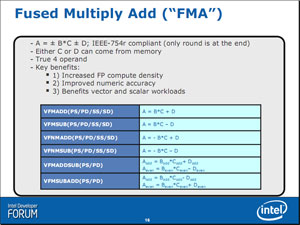

Prévu pour 2012 au plus tôt, la famille de CPU Haswell succédera à l'architecture Sandy Bridge. Gravés en 22 nm, ils devraient inclure 8 cœurs par défaut, une toute nouvelle architecture de caches, des mécanismes "révolutionnaires" d'économie d'énergie ainsi que la possibilité d'embarquer des coprocesseurs de traitement vectoriels dans un package unique. Côté jeu d’instructions, le serpent de mer FMA (Fused Multiply-Add), qui permet d’effectuer simultanément une opération de multiplication et une addition via la même instruction, devrait être implémenté.

Aucune autre information n'a filtré sur Haswell, mais vu que nous parlons d'un CPU qui sortira dans 3 générations, ce n'est pas étonnant. Le design du processeur n'en est encore qu'aux premiers balbutiements.

- Larabee

S'il y avait un sujet tabou chez Intel lors de cet IDF, c'était bien le « GPU » Larabee. Pour rappel, Larabee est une puce massivement multi-cœur (plusieurs dizaines), conçue pour effectuer des opérations vectorielles à très grande vitesse. Bien qu’Intel n’ai pas dit un seul mot sur ce composant lors de l’IDF, il parait clair que Larabee se heurte à deux problèmes.

Tout d’abord, un problème de positionnement sur le marché. Prévu pour être une sorte de GPU haut de gamme, il ne peut se permettre de ne pas offrir les performances des dernières GeForce et autres Radeon. Un pari risqué. Ensuite, un problème de timings : les premiers prototypes de Larabee ne sortiront pas des chaines de fabrications avant Mars-Avril 2009, soit une commercialisation fin 2009 au mieux.

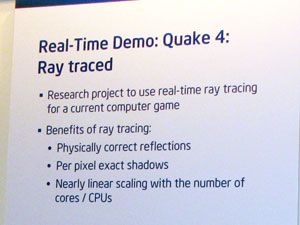

Enfin, reste la question la plus cruciale : même si Larabee dispose d’une puissance théorique énorme, encore faut-il l’exploiter correctement et dans ce domaine, les développeurs de jeux vidéo ne font pas spécialement d’efforts. Heureusement, sur ce point, Intel a présenté une esquisse de solution assez séduisante : le ray-tracing. L’idée est ici de faire du rendu d’image en temps réel par ray-tracing, une technique qui permet une excellente qualité de rendu, mais qui reste extrêmement gourmande en puissance de calcul. Heureusement, les algorythmes utilisés peuvent facilement exploiter plusieurs dizaines de cœurs, si vous voyez ou je veux en venir.

Intel a donc fait la démonstration du moteur de Quake 4 fonctionnant en ray-tracing :

Grace à deux processeurs Quad Core haut de gamme actuel, la démo tournait à 90 fps en 1280x960. De quoi espérer un Crysis fluide en Full HD avec l'hypothétique Larabee ? Fort possible...

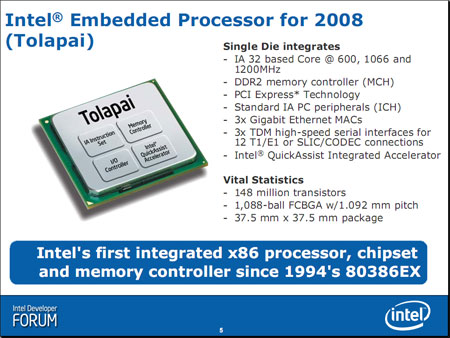

- Tolapai

Bien que quasi-vampirisés par le lancement des processeurs Atom lors de cet IDF, l’arrivée des SOC (System On a Chip) d’Intel, connus sous le nom de code Tolapai, est imminente. Ces processeurs sont basés sur un cœur Dothan (Pentium M) cadencé à 600 MHz, 1066 MHz ou 1200 MHz et embarquent un chipset complet supportant la DDR2, le PCI Express, des ports Gigabit Ethernet ainsi que le support pour les périphériques de base.

Tolapai est l'arme d'Intel pour rivaliser avec les puces ARM dans les systèmes embarqués comme les routeurs et autres NAS. L'un des ingénieurs en charge du projet nous a également confié que Tolapai était à l'étude chez certains fournisseurs d'accès à Internet comme cœur pour les Box de nouvelles générations. Parmi ceux-ci figureraient un français...

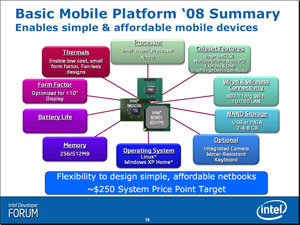

- Atom

Au cœur du concept de MID et Netbook d’Intel (voir page suivante), on trouvera un processeur Atom. Celui-ci se décline en deux packagings, selon la taille disponible sur la carte mère. On trouvera ainsi les Z500, dans un format de 13mm x 14 mm adaptés aux MIDs et le N270, de 22 mm x 22 mm, pour les Netbook.

Ces processeurs sont basés sur l’architecture Core gravés en 45 nm. Ils sont équipés de 512 Ko de cache L2, d’un FSB de 100 ou 133 MHz (soit 400 et 533 QDR) et d’une fréquence comprise entre 800 MHz et 1.86 GHz. Certaines versions supportent même l’Hyper Threading. La prouesse réside dans leur dissipation thermique comprise entre 650 mW pour la version Z500 à 800 MHz et 2.4 Watts pour la déclinaison 1.86 GHz.

Le processeur Atom et son chipset sont parfaitement capable de fonctionner sans aucun radiateur.