| Sommaire: |

![]()

C3 : Caractéritiques

Il existe actuellement 6 (bientôt 7) version du VIA C3 que nous allons récapituler dans un tableau. Commençons par les première déclinaisons du C3 :

| Core | C5A - Samuel |

C5B - Samuel 2 |

C5C - Ezra |

C5N - Ezra-T |

| Cache L1 | 128kB (2x 64kB) |

128kB (2x 64kB) |

128kB (2x 64kB) |

128kB (2x 64kB) |

| Cache L2 | 0 kB |

64kB |

64kB |

64kB |

| Fréquence du bus | 100/133MHz |

100/133MHz |

100/133MHz |

100/133MHz |

| Finesse de gravure | 0.18 µm |

0.15 µm |

0.13 µm |

0.13 µm |

| Taille du die | 75 mm˛ |

52 mm˛ |

52 mm˛ |

56 mm˛ |

| Nombre de transistors | 11.3 Millions |

15.2 Millions |

15.4 Millions |

15.5 Millions |

| Autre | MMX, 3DNow! |

MMX, 3DNow! |

MMX, 3DNow! |

MMX, 3DNow! |

| Vitesse FPU | 1/2x Core |

1/2x Core |

1/2x Core |

1/2x Core |

| Profondeur du pipeline | 12 étages |

12 étages |

12 étages |

12 étages |

| Produit par | TSMC |

TSMC |

TSMC |

TSMC |

Et passons ensuite aux versions plus récentes :

| Core | C5XL - Nehemiah

(stepping 0 ŕ 7) |

C5P - Nehemiah (stepping 8 et plus) |

C5J (C7) - Esther (2005) |

| Cache L1 | 128kB (2x 64kB) |

128kB (2x 64kB) |

? |

| Cache L2 | 64kB |

64kB |

> 64kB |

| Fréquence du bus | 100/133MHz |

100/133MHz |

800MHz (bus Pentium-M) |

| Finesse de gravure | 0.13 µm |

0.13 µm |

90 nm |

| Taille du die | 52 mm˛ |

47 mm˛ |

Approximativement 30 mm˛ |

| Nombre de transistors | 20.5 Millions |

20.4 Millions |

? |

| Autre | RNG, MMX, SSE |

2x RNG, ACE, MMX, SSE, SMP |

2x RNG, ACE, NX-Bit, SHA-1, SHA-256,

MMX, SSE1/2/3, SMP |

| Vitesse FPU | 1x Core |

1x Core |

? |

| Profondeur du pipeline | 16 étages |

16 étages |

? |

| Produit par | TSMC |

TSMC |

IBM |

|

Le C5A a été une véritable catastrophe au niveau des performances dû a son absence totale de cache L2 (qui a parlé du Celeron 300?) et a donc vite été abandonné au profit du C5B. La différence entre le core Ezra et Ezra-T vient du support des cartes mère pour Pentium III Tualatin. Les C5A, C5B, C5C et C5N n'ont somme toute été que des évolutions mineures d'une architecture de base avec le handicap de la FPU fonctionnant à la moitié de la vitesse du core. Le C5XL représente donc théoriquement une avancée majeure dans le domaine du multimédia avec sa FPU à pleine vitesse et le support des instructions SSE à la place du 3DNow!. Le C5P est basiquement un C5XL retravaillé: on lui a ajouté une unité RNG et une unité ACE et une meilleure optimisation du core a permis de rétrécir la surface totale à 47mm² au lieu des 52 mm². Ceci permet de consommer moins d'énergie à fréquence égale. Selon les prévisions de VIA, le C5J devrait avoir une consommation électrique équivalente à la moitié de celle d'un C5P à fréquence égale et débuter sa carrière à 2GHz. |

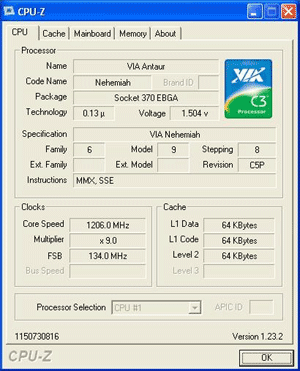

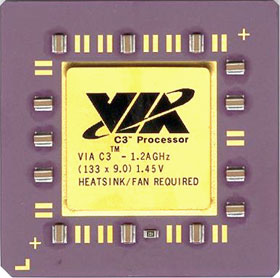

Les principales caractéristiques de notre C5P sont:

- Support total des instructions MMX

- Support total des instructions SSE

- Compatible x86 à 100%

- Cache L1 de 2x 64kB (Data et Instruction) à 2 voies

- Cache L2 de 64kB à 16 voies

- Fréquence de bus de 133MHz

- Un des plus petits cores x86 du monde avec seulement 47 mm² ce qui promet d'avoir une dissipation thermique maximale annoncée de 18.4W à 1200MHz bien que certaines applications comme des "virus thermiques" comme les appellent VIA puissent aller au-delà.

- Deux unités RNG (Random Number Generator) hardware

- Une unité ACE (Advanced Cryprography Engine) hardware

- Supporte le mode SMP jusqu'à 4 processeurs

- Prédiction de branchement StepAhead

Les mémoires caches sont du type exclusif ce qui nous donne un total de 192kB de cache dans le CPU ce qui est identique à un Duron. Jetez un coup d'oeil à l'excellente explication sur les caches fournie lors de la parution de l'article sur l'Athlon64.

|

|

Comme nous l'avons dit précédemment, il y a 5 nouveautés majeures dans le core C5P:

- L'augmentation de la profondeur du pipeline de 12 vers 16 étages

a sans doute été faite dans l'optique de pouvoir monter

en fréquence ce qui est de bonne augure pour l'overclocking.

- Le GRAND point faible de la gamme C3 a été corrigé:

l'unité de calcul en virgule flottante (FPU) est désormais

cadencée à la même vitesse que le core, ceci devrait

permettre un gain de performances non négligeable dans bon nombre

d'applications.

- La suppression de l'unité 3DNow! d'AMD au profit du SSE d'Intel

est sans doute dû au manque d'intérêt des développeurs

pour le 3DNow!. On peut se poser la question du pourquoi ne pas avoir

gardé les 2 unités dans le core? VIA faisant sa publicité

sur le faible dégagement calorifique de ses processeurs (donc

directement dépendant du nombre de transistors) ils ont sans

doute jugés superflus de garder l'unité 3DNow!

- L'intégration de deux unités RNG (Random Number Generator)

directement au coeur du processeur.

- L'intégration d'une unité ACE (Advanced Cryptographic Engine) directement au coeur du processeur.